# The Future Device - Tunnel Field Effect Transistor A survey

Helen Ramya Bharathi R

ME Scholar, Department of ECE, PSNA College of Engineering and Technology, Dindigul, Tamilnadu, India.

T. Evangeline Santhia

ME Scholar, Department of ECE, PSNA College of Engineering and Technology, Dindigul, Tamilnadu, India.

# Dr.P.Karthikeyan

Asst. Professor, Department of ECE, PSNA College of Engineering and Technology, Dindigul, Tamilnadu, India.

Abstract – The down-scaling of regular MOSFETs has prompted a looming power emergency, in which static power utilization is ending up noticeably too high. Keeping in mind the end goal to enhance the vitality productivity of electronic circuits, little swing switches are intriguing contender to supplant or supplement the MOSFETs utilized today. TFETs, which are gated p-i-n diodes whose on-current rises up out of band-to-band burrowing, are engaging new devices for low-control applications due to their low off-current and their potential for a little subthreshold swing. Aside from every one of these points of interest TFET experiences low ON current. So to enhance this low ON current many gate engineering structures have been proposed. This paper clarifies every one of the strategies which are utilized till now and furthermore clarifies device structure and execution assessment.

Index Terms – TFET (Tunnel Field Effect Transistor), MOSFET (Metal Oxide Semiconductor Field Effect Transistor), ON current, low power.

# 1. INTRODUCTION

TFET has been wound up being a proper gadget to supplant MOSFET. Because of its in-built tunnel, it doesn't impacted by Short Channel Effects (SCEs).TFET has incredible properties, for instance, cut down subthreshold swing i.e,.>60 mV/decade, which is thought to be a physical impediment in MOSFET. Moreover TFET exhibits little leakage current, in the extent of femto amperes (fA). Beside each one of these points of interest, TFET encounters low ON current (Ion). To extend this  $I_{ON}$  various Gate Engineering structures have been proposed.

So this paper is all about various gate engineering structures which are used to improve ON current.

# 2. TUNNEL FIELD EFFECT TRANSISTOR

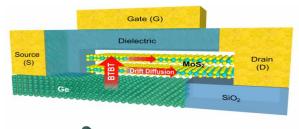

2.1 Structure

The source considered Tunnel Field Effect Transistor is p-i-n diode. TFET is on a very basic level a gated turned around one-sided p-i-n diode in which tunneling of the transporter

occur among one band to another band. The minimum complex construct of TFET holds vivaciously doped source and drain region, which are doped with backwards impurities impacts and channel region is considered of trademark sort. By appertaining the right biasing the tunneling of the transporter from source-channel intersection happens.

Figure 1 Structure of TFET

- 2.2 Priciples of operation

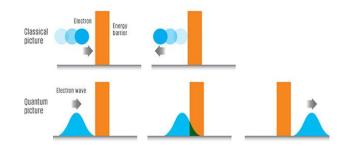

- 2.2.1 Quantum Tunneling

Electrons and holes comply with the law of quantum mechanics, which implies they possess fluffy indeterminate size. When an energy barrier has a thick beneath 10nm, there is a little however non-zero likelihood that electron can move. In TFET, this likelihood is supported by applying a voltage to the gate.

Figure 2 Quantum Tunneling

This promotes the conduction band in the source and valence band in the channel to cover. This affords a tunneling window. This can be done when an energy is covered by voltage. By boosting the probability of quantum tunneling mechanism current conduction will be improved.

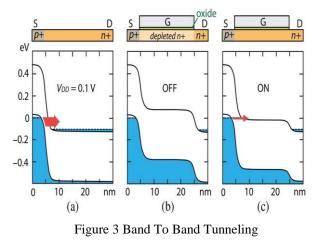

#### 2.2.2 Band to Band Tunneling (BTBT)

This happens when the device is in Reverse bias. This shapes a restricted tunneling barrier. So there will be an expansive electric field. When the gate voltage is zero there will be a wide obstruction at the source-channel junction. When gate voltage gets expanded the bands in the intrinsic area are pushed down making a channel that starts to appear. So at long last when there is a high Vgs the width of the energy barrier gets lessened so the ON current gets expanded.

#### **3. LITERATURE SURVEY**

3.1 Analytical modeling and simulation of single-gate SOI TFET for low-power applications

#### Theme:

In the paper [1], the authors offered two-dimensional (2-D) analytical model of the single-gate (SG) silicon-on-insulator (SOI) tunnel field effect transistors (TFETs). Here the parabolic approximation technique is utilized to understand the 2-D Poisson condition by appropriate limit conditions. Explanatory expressions for surface potential and electric field are inferred. The legitimacy of the propound model is tried for gadget cut down to 18-nm length and the logical outcomes are contrasted with Technology Computer Aided Design (TCAD).

#### Model:

Whereas the n-type device, the drain region is of n-type substantial, the source region is of p-type substantial and the channel region is an intrinsic substantial. Proportionate circuit of a TFET is comprised of straight and uninvolved components that hold the greater part of the electrical attributes of the device. The back subordinate of the covered oxide is grounded. Being the consistence of the Buried Oxide (BOX) layer is little to be in any way examined, the potential over this district is thought to be zero.

# Performance validation:

Expanding the positive gate voltage, the vitality boundary among the p+ source region and intrinsic region gets decreased. Because of this lessening of boundary diameter, electrons in the valance band passage to the conduction band of intrinsic district. At that point by the drift diffusion system, electrons have a tendency to go to the drain region out of the intrinsic region. The barrier diameter begins to immerse at high  $V_{GS}$ . For a little one-sided voltage of  $V_{DS}$ , charge bearers can tunnel through the vitality boundary at the source/intrinsic bond. For bigger  $V_{DS}$ , immersion happens fundamentally the same as a MOSFET.

#### Outcome:

Demonstrated that TFET indicates less SCE (Short Channel Effects) than MOSFET and furthermore infer that the proposed model can end up being a profoundly proficient substituting answer for the current MOSFET gadget.

3.2 Compact Analytical Model of Dual Material Gate

Tunneling Field-Effect Transistor Using Interband Tunneling and Channel Transport

#### Theme:

In the paper [2], the creators have developed a 2-D Analytical model for surface potential and drain current for a Dual Material Gate (DMG) Tunneling Field Effect Transistor (TFET). This model fuses the effect of exhaust voltage, gate metal work function, oxide thickness, silicon film thickness, without expecting a totally depleted channel, effect of charge social occasion at the interface of the two gates and the assortment in the tunneling volume with the associated gate voltage. The exactness of the model is taken a stab at using 2D numerical model.

#### Model:

The source and drain is inclusive of exceptionally doped ptype and n-type. The middle of the channel region is together with a reasonably doped n-type layer. SiO<sub>2</sub>is utilized as the gate dielectric. The gate comprises of two materials with gate lengths with two distinctive work functions. In light of the positive or negative potential connected to the gate terminal, the gadget carries on as n type TFET and p type TFET separately. In the event that a positive gate voltage is connected, the transistor carries on as a n-TFET furthermore, a negative gate voltage is connected, the transistor acts as a p-TFET. Performance validation:

At low estimations of  $V_{DS}$ , the gate predisposition induces a collection of devices in the channel area. Here this prompts diminish of the channel resistance. In this manner the channel diameter is decreased which thus manufactures the electric field over the tunneling crossing point, inciting a quick augmentation in the drain current. As the gate voltage assembles, the potential in the delicately doped area increases. There is a modification of potential besides the channel. In this way the gate slant has high effect on tunneling current at source side.

#### Outcome:

Finally, this can be inferred that the DMG construction gives extensive variety of advantages to the TFET execution. The outcomes unmistakably exhibit the magnificent insusceptibility contrary to SCE (Short Channel Effects) offered by the DMG system in the time of diminishing channel length.

3.4 Impact of Electric field Distribution on the performance of Dual Material Gate Work function Engineered Surrounding Gate Nanowire Tunnel FETs

#### Theme:

In the paper [3], the authors have defined a two dimensional (2D) expository model for examining the electric field dissemination of a p-type Dual Material Surrounding Gate Nanowire tunneling Field Effect Transistor (DMSG-NWTFET). This nanostructure of DMSG Tunnel FET consolidates the benefits of encompassing gate and the two distinctive gate material work capacities. A stage change of potential along the channel is gotten, which screens the source region from the drain potential varieties, accordingly decreasing the deplete control over the channel. This device appears enhanced electrical qualities and in light of the gate built nanostructure, there is considerable decreasing of short channel impacts and hot transporter impacts.

Model:

The gate terminal is made of two materials of various work capacities. These two distinct materials are stored over separate gate lengths. For p-channel TFET, the gate material at the source edge has the most noteworthy work function what's more, the material found in the drain end is with the most reduced work function.

# Performance validation:

The distinctive work elements of two metal gates guarantee lessening in the short channel impacts (SCEs). As the drain to source voltage ( $V_{ds}$ ) expands, the potential close to the deplete region additionally increments however the region towards the source and channel is totally screened from the drain

potential varieties. This screening impact has demonstrated that, the drain potential varieties have no encounter on the tunneling rate at the source marginal. There is a pinnacle electric field got at the source side which is a result of the higher work material at the source side of Dual Material GAA Nanowire TFET. By decreasing the gate oxide thickness, the drain potential varieties are stifled totally, which thusly makes the Nanowire TFET structure more invulnerable against the short channel impacts (SCEs).

#### Outcome:

The outcomes demonstrate that the pinnacle electric field at the drain side is stifled and this can be deciphered as a minimization of hot bearer impacts. This causes the electrons to tunnel from valence band to conduction band effortlessly and brings about an expanded tunneling current. In this manner, when we enter profound into the sub-nanometer region, the proposed work appears a fantastic resistance against short channel impacts, and can be utilized as a part of many low power applications and in memory gadgets.

3.4 A Numerical Study on Graphene Nanoribbon

Heterojunction Dual-Material Gate Tunnel FET

#### Theme:

In the letter [4], the authors presented a passage FET (TFET) consolidating both Graphene Nano Ribbon (GNR) Hetero Junction (HJ) and gate work (WF) designing is examined among the mathematical reenactment. The most minimal subthreshold swing is littler than 15 mV/decade what's more, the ON state current (ION) ranges to 1.7  $\mu$ A with gadget width littler than 3 nm. The channel width is all around lessened with the Dual Material Gate (DMG) inspiring the ON current. The channel including a wide vitality hole (Eg) GNR can successfully lessen the leakage current by OFF state at its length is 13 nm.

#### Model:

The GNRs situated at XZ plane in TFET and the conveyance bearing is as companion with Z hub. Here, three sorts of GNR HJ-DMG TFETs are utilized. The aggregate breath of TFET in is 20 nm. The channel is 10 nm and the source/drain region is 5 nm each. The Double gate form is embraced also the density of SiO2 layer on each side is 1 nm. The SiO<sub>2</sub> layers binding the entire GNR domain. Together with the limited  $E_g$ assets, the channel width can be very much decreased. The  $E_g$ of the GNR in the rest some portion of channel and the drain region is 1.27 eV which is substantially bigger than the past one so as to limit the off state current.

Performance validation:

In this manner, the band twisting predominantly happens inside the region. Together with the tight  $E_g$  property, the

# International Journal of Emerging Technologies in Engineering Research (IJETER) Volume 5, Issue 4, April (2017)

www.ijeter.everscience.org

channel width can be all around diminished. The Eg of the GNR in the rest some portion of channel and the drain region is 1.27 eV which is considerably bigger than the past one keeping in mind the end goal to limit the off state current. The huge doping focus in the drain region is utilized to control the ambipolar conduct. The channel is undoped. At the point when the Vg expanding to 0.2 V the streams in all TFETs are expanded strongly and the transporter tunneling over the channel obstructions is supported.

#### Outcome:

The amazingly low SS, huge I<sub>on</sub>, and moderately straightforward topological form of the proffered TFET demonstrated that it is an appropriate hopeful in low power utilization.

3.5 Double-Gate Tunnel FET with High-ĸ Gate Dielectric

# Theme:

In the paper [5], the authors proposed a innovative outline for a Double Gate Tunnel field-impact transistor (DG Tunnel FET), DG Tunnel FET devices, which are promoting a high-k gate dielectric, are check out utilizing practical frame specifications, demonstrating an ON-present as high as 0.23 mA for an gate voltage of 1.8 V, an OFF-current of lower 1 fA, an enhanced normal subthreshold swing of 57 mV/dec, and a least point incline of 11 mV/dec. In addition, a particle/I<sub>off</sub> distribution of more than  $2 \times 1011$  is arrived for recreated devices with a gate length of 50 nm, which exhibits that the Tunnel FET is a assuring contender to carry out exclusive to anything ITRS deep backup control switch enactment.

# Model:

The explored device form is a parallel n-type TFET in a fragile silicon layer, isolated in distinction to the substrate over a dielectric layer. The major layout is a gated p-i-n diode. The tunneling arises in this device within the intrinsic and p+ region. To work DG gadgets, the p-i-n diode is switched onesided the source is grounded, and a positive voltage is associated with the drain and a voltage is associated with the gate(s).

# Performance Validation:

Significantly unrivaled ON-present and reduced subthreshold swing can be gotten by the vigilant choice of a gate dielectric. Current additions as the gate dielectric steady augmentation. The diminished fruitful oxide thickness gave by these dielectrics offers a response for the low ON current issue experienced by some present TFETs at great voltages. The OFF current is under 1 fA for DG, a high-k gate dielectric, furthermore, an enhanced silicon body thickness. The DG and high- $\kappa$  dielectric raise ON-current to 0.23 mA at V<sub>g</sub> = 1.8 V and give a contrasting change in the typical subthreshold swing, as low as 57 mV/dec, and a base point swing of 11 mV/dec. In extension, the subthreshold swing for settled characteristics of Vg remains practically unaltered as temperature augmentations.

# Outcome:

The researched Tunnel FET demonstrated enhanced attributes along with superior ON current what's more, a lessened subthreshold swing TFET's assuring conduct causes a solid competitor to supplement or supplant MOSFET innovation, especially for LSTP purposes. High-κ dielectrics bring extra difficulties, for example, the restrictions of delicate and firm dielectric disruption. Relying on the qualities of created highκ dielectric seams, it might be important to constrain connected gate voltages farther than what is accounted for here.

# 4. OBSERVATION FROM THE SURVEY

Because of inherent passage in TFET, it does not experience Short Channel Effect (SCE). And furthermore the subthreshold swing of TFET is >45 mV/decade. So it has been demonstrated that TFET is the best swap for MOSFET. Aside from every one of these benefits, TEFT experiences low ON current. To enhance this low on current many gate enginerring structures have been done. So by utilizing the appropriate gate materials with various workfunction the execution gets increased. So in all the explanatory model three parameters are broke down specifically surface potential, electric field, drain current. The different work elements of two gate materials guarantee decrease in the short channel effects (SCEs). As the drain to source predisposition (V<sub>ds</sub>) expands, the potential close to the drain region likewise increments yet the region towards the source and channel is totally screened from the drain potential varieties. This screening concussion has demonstrated that, the drain potential varieties have no appulse on the tunneling rate at the source marginal. At the point when gate voltage changes, the adjustment in the sidelong electric field is less at the drain side than looked at the source side. Diminishing the gate oxide thickness, the drain potential varieties are smothered totally, which thusly makes the TFET structure more insusceptible against the short channel effects (SCEs).

# 5. TFET: DEVICE AND DESIGN CHALLENGES

# 5.1 Scaling Demands:

In TFET, beside limited bandgap as well as enlarged gate length, ambipolar spillage is the principle explanation behind SS debasement what's more, high-IOFF. Be that as it may, in compressed gate breath TFETs, the more concise tunneling way amongst source and drain bothers guide source-to-drain tunneling leakage, while the expanded bandgap because of repression decreases the ambipolar leakage issue. Dissimilar to in the MOSFET, oxide scaling does not enhance short

channel effects in the TFET essentially; rather body density scaling is the most critical specification at the point when the device geometry is altered against double gate to a gate allaround. Despite the fact that MOSFET subthreshold qualities don't enhance since they are effectively near perfect, the TFET enhances fundamentally. Subsequently, the body thickness necessity is significantly more tightly for TFET than MOSFET, with 3nm nanowire prescribed for  $L_G = 9nm$ . As  $L_G$  scaling proceeds with, two-dimensional semiconductors with inherently unrivaled electrostatics might be the greater decision for TFETs.

#### 5.2 Circuit Formation Effects

The asymmetry of TFETs additionally has outcomes for circuit format thickness. Logic gates typically desire two or more N-type or P-type devices to be associated in arrangement. This circuit course of action has an effective design in a MOSFET innovation in light of the fact that the source-to-drain associations of two arrangement MOSFETs can share a solitary contact. This format, be that as it may, is impractical with TFETs on the grounds that the source drain contacts utilize distinctive materials. As a result, additional space is expected to accomplish a progression of two TFETs source-to-drain association, decreasing the thickness of essential TFET logic cells by a sum emphatically reliant on the particular plan rules of the innovation hub. In spite of the fact that a collinear transistor design is feasible for framework of TFET circuits, the indicated passage has its own challenges including the plan and manufacture of the base contact. The ordinary even transistor engineering, which is a less troublesome way to deal with execute concerning the cutting edge CMOS gauge.

#### 5.3 Consequences for Uni-directional Conduction

As opposed to MOSFETs which have symmetric I-V conduct, the TFET's source-channel-drain P-I-N structure comes about in immeasurably unique I-V qualities with positive or negative V<sub>DS</sub> predisposition. A N-TFET with low negative V<sub>DS</sub> inclination has low conduction on the grounds that the natural P-I-N diode is forward one-sided underneath its turnon voltage. A practically equivalent to condition exists for the P-TFET under positive  $V_{DS}$ . This  $V_{DS}$  reliance brings about devices that exclusive considerably direct with a solitary  $V_{DS}$ extremity. As an outcome, for circuits whose operation requires bidirectional conduction, elective topologies are required. The V<sub>DS</sub> reliance can bring about unobtrusive circuit contrasts too. In both CMOS and TFET logic, exchanging voltages on wires and transistor terminals can capacitively exchange charge and make transient voltages. In CMOS, the charge exchanged can be released however a MOSFET under both positive and negative drain source inclinations, restricting commotion voltage greatness and term.

However, in TFET logic, when the commotion voltage forward inclinations its P-I-N structure (e.g. negative V<sub>DS</sub> for N-TFET), the TFET has low conduction and can't rapidly scatter the charge. The voltage on the flag may move generously above V<sub>DD</sub> or subterranean and may bring about planning blunders what's more, unwavering quality concerns if not legitimately took care of by plan strategies. Unwavering quality concerns require additionally consider yet are insignificant in light of TFET's lower supply voltages analyzed to those for regular CMOS. In different circuits, logic gates can profit by unidirectional conduction. TFET's conductivity asymmetry with V<sub>DS</sub> empowers outline of new MUX circuits with less transistors, bring down power and preferable execution over CMOS executions. It stays to be checked whether benefits from such circuits can adjust for alternate issues created by source and drain asymmetry. However, the TFET's exceptional I-V qualities open up new roads for circuit creators to make novel and huge changes.

#### 6 CONCLUSION

In this work, an entire overview on the progress of Tunnel Field Effect Transistor (TFET) is presented. Innovation which shows that to some degree positional adjustment of the gate terminal of TFETs makes the development more insignificant and sensible over standard MOSFET. The thought of Gate Engineering in TFETs discussed in this compact study can be utilized to cover the ambipolarity of TFET and to fulfill greater ON current.

#### REFERENCES

- T.S. Arun Samuel, N.B. Balamurugan, S. Bhuvaneswari Sharmila & K.Padmapriya, "Analytical modelling and simulation of single-gate SOI TFET for low-powerapplications," International Journal of Electronics, DOI:10.1080/00207217.2013.796544 21, June 2013.

- [2] Rajat Vishnoi and M. Jagadesh Kumar, "Compact Analytical Model of Dual Material Gate Tunneling Field-Effect Transistor Using Interband Tunneling and Channel Transport," IEEE, vol. 61,no. 6, pp. 1936-1942, Jun 2011.

- <sup>[3]</sup> G.Lakshmi Priya, Dr.N.B.Balamurugan and D.Saraswathi, "Impact of Electricfield Distribution on the performance of Dual Material Gate Work function Engineered Surrounding Gate Nanowire Tunnel FETs," International Journal of Applied Engineering Research, ISSN 0973-4562 Vol. 10 No.1 (2015) pp. 1018-1023, Jan 2015.

- [4] Yawei Lv, Qijun Huang, Hao Wang, Jin He and Sheng Chang, "A Numerical Study on Graphene Nanoribbon Heterojunction Dual-Material Gate Tunnel FET," IEEE electron device letters, vol. 37, no. 10, october 2016.

- [5] Kathy Boucart and Adrian Mihai Ionescu, "Double-Gate TunnelFET With High-κ Gate Dielectric," IEEE transactions on electron devices, vol. 54, no. 7, july 2007.

- [6] J.H. KaiWang, S. Wu, T.K. Chiang, M.S. Lee, A new two-dimensional analytical threshold voltage model for short channel triple material surrounding-gate metal oxide semiconductor field effect transistors, Jpn. J. Appl. Phys. 51,pp. 054-301,2012.

- [7] E.G. Ioannidis, A. Tsormpatzoglou, D.H. Tassis, C.A.Dimitriadis, G. Ghibaudo, J. Jomaah, Effect of localized interface charge on the threshold voltage of short channel undoped symmetrical double-gate MOSFETs, IEEE Trans. Electron. Dev. 58,pp. 433- 440,2011.

- [8] Sharma, S.K. Vishvakarma, "Precise analytical model for short channel cylindrical gate (CylG) gate-all around(GAA) MOSFET", Solid State Electron. 86,pp. 874,2013.

- [9] X. Liang and Y. Taur, "A 2-D analytical solution for SCEs in DG MOSFETs", Electron Devices, IEEE Transactions on, vol. 51, Issue 9, pp. 1385-1391,2004.

- [10] Cerdeira, O. Moldovan, B. Iniguez and M. Estrada, "Modeling of potentials and threshold voltage for symmetric doped double-gate MOSFETs"; Solid-State Electronic, vol. 52, Issue 5, pp.830-37,2008.

- [11] Y.C. Yeo, T.J. King, C. Hu, MOSFET gate leakage modeling and selection guide for alternative gate dielectrics based on leakage considerations, IEEE Trans. Electron. Dev. 50,pp. 1027,2003.

- [12] H. A. E. Hamid, J. R. Guitart and B. Iniguez, "Two-Dimensional Analytical Threshold Voltage and Subthreshold Swing Models of Undoped Symmetric Double-Gate MOSFETs", ElectronDevices, IEEE Transactions on, vol.54, Issue 6, pp. 1402-1408, 2007.